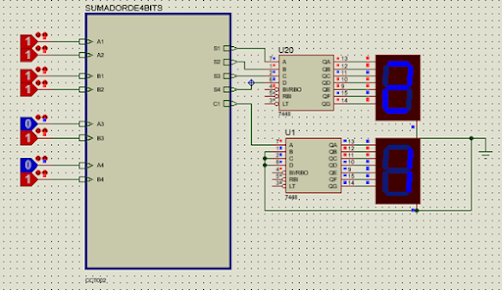

Sumador de 4 bits

Sumador de 4 bits

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if

instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity sumadorde4bits is

Port ( a1 :

in STD_LOGIC;

a2 :

in STD_LOGIC;

a3 :

in STD_LOGIC;

a4 :

in STD_LOGIC;

b1 :

in STD_LOGIC;

b2 :

in STD_LOGIC;

b3 :

in STD_LOGIC;

b4 :

in STD_LOGIC;

s1 :

out STD_LOGIC;

s2 :

out STD_LOGIC;

s3 :

out STD_LOGIC;

s4 :

out STD_LOGIC;

ci :

out STD_LOGIC);

end sumadorde4bits;

architecture Behavioral of sumadorde4bits is

component medio_sumador is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c :

out STD_LOGIC;

s: out STD_LOGIC);

end component;

component sumadorcompleto is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

cin :

in STD_LOGIC;

s1 :

out STD_LOGIC;

cout :

out STD_LOGIC);

end component;

SIGNAL cx, cy, cz :STD_LOGIC;

begin

U0: medio_sumador PORT MAP (a1, b1, s1, cx);

U1: sumadorcompleto PORT MAP (a2, b2, cx, s2,cy);

U2: sumadorcompleto PORT MAP (a3, b3, cy, s3,cz);

U3: sumadorcompleto PORT MAP (a4, b4, cz, s4,ci);

end Behavioral;

.png)

Comentarios

Publicar un comentario