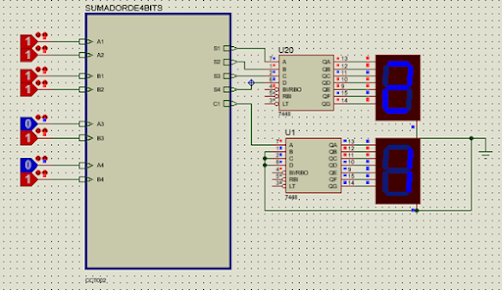

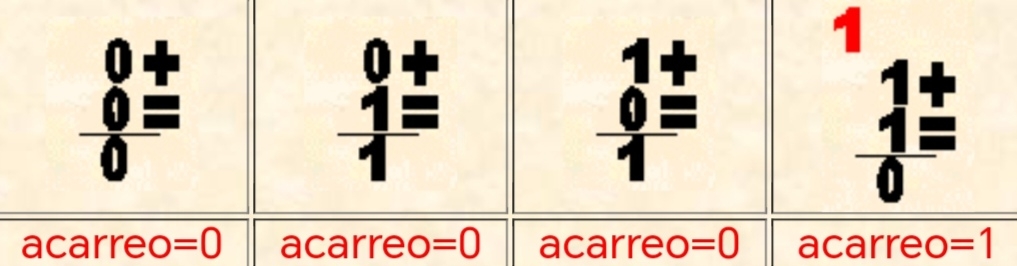

Sumador de 2 bits El sumador binario es un circuito capaz de hacer la suma algebraica entre dos números binarios con un bit cada uno, que hace que la suma de dos bits a la vez, es decir, dos dígitos binarios a la vez. Primero vemos un semi sumador , es decir, un circuito que recibe como entrada dos dígitos binarios y da en salida a su suma, más el acarreo. Se toma nota de que el acarreo es 1 solamente cuando ambos bits son 1; entonces: 1 + 1 = 0 y acarreo de 1. En otros casos, las reglas son las mismas que el sistema decimal. Podemos hacer una tabla de verdad de la suma binaria. Donde A y B son los dos bits de entrada, S es la suma de los dos bits de entrada; C es el acarreo de la suma realizada. La suma S corresponde a una puerta lógica EXOR; el acarreo C corresponde a una puerta lógica AND. ( para el acarreo no usamos la letra A, pero usamos la C, que es el acarreo en Inglés, es decir Carry ). entity sumadorde2bitscomponentes is ...

.png)

.png)